## **79C2040** 20 Megabit (512K x 40-Bit) FFPROM MCM

### **FEATURES:**

#### 512k x 40-bit EEPROM MCM

- Rad-Pak® radiation-hardened against natural

- space radiation

- Total dose hardness:

- >100 krad (Si)

- Dependent upon orbit

- Excellent Single event effects

- SEL<sub>TH</sub> > 120 MeV/mg/cm<sup>2</sup>

- SEU > 90 MeV/mg/cm<sup>2</sup> read mode

- SEU = 18 MeV/mg/cm<sup>2</sup> write mode

- High endurance

- 10,000 cycles/byte (Page Programming Mode)

- 10 year data retention

- Page Write Mode: 128 Dword Page

- High Speed:

- 150 and 200 ns maximum access times

- · Automatic programming

- 10 ms automatic Page/Dword write

- Low power dissipation

- 375 mW/MHz active current

- -3. 2 mW standby current

### **DESCRIPTION:**

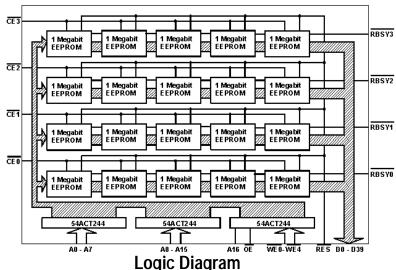

Maxwell Technologies' 79C2040 multi-chip module (MCM) memory features a greater than 100 krad (Si) total dose tolerance, dependent upon orbit. Using Maxwell Technologies' patented radiation-hardened Rad-Pak® MCM packaging technology, the 79C2040 is the first radiation-hardened 20 megabit MCM EEPROM for space application. The 79C2040 uses twenty 1 Megabit high speed CMOS die to yield a 20 megabit product. The 79C2040 is capable of in-system electrical byte and page programmability. It has a 128 word page programming function to make the erase and write operations faster. It also features Data Polling and a Ready/Busy signal to indicate the completion of erase and programming operations. In the 79C2040, hardware data protection is provided with the RES pin, in addition to noise protection on the WE signal and write inhibit on power on and off. Software data protection is implemented using the JEDEC optional standard algorithm.

Maxwell Technologies' patented Rad-Pak® packaging technology incorporates radiation shielding in the microcircuit package. It eliminates the need for box shielding while providing the required radiation shielding for a lifetime in orbit or space mission. In a GEO orbit, Rad-Pak provides greater than 100 krad (Si) radiation dose tolerance. This product is available with screening up to Maxwell Technologies self-defined Class K

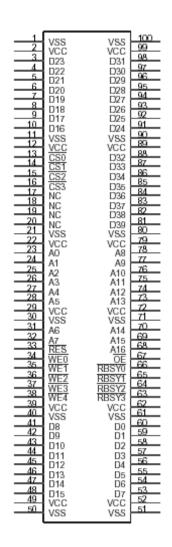

## PINOUT DESCRIPTION

| 1, 11, 21, 30, 40, 50,<br>51, 61, 71, 80, 90, 100 | VSS - Ground               |

|---------------------------------------------------|----------------------------|

| 2, 12, 22, 29, 39, 49,<br>52, 62, 72, 79, 89, 99  | VCC - Positive Supply      |

| 60 - 53, 41 - 48, 10 -<br>3, 91 - 98, 88 - 81     | D0 to D39 Data I/O         |

| 13, 14, 15, 16                                    | CS0\ - CS3\ Chip Enable    |

| 23 - 28, 31, 32, 78 -73,<br>70 - 68               | A0 to A16 Address Inputs   |

| 33                                                | RES\ - Reset               |

| 34 - 38                                           | WE\0 - WE\4 Write Enables  |

| 66 - 63                                           | RBSY\0 - RBSY\3 Ready/Busy |

| 67                                                | OE∖ - Output Enable        |

Table 1. 79C2040 Absolute Maximum Ratings

| Parameter                   | Symbol           | Min               | Түр | Max | Unit  |

|-----------------------------|------------------|-------------------|-----|-----|-------|

| Supply Voltage              | V <sub>CC</sub>  | -0.6              |     | 7.0 | V     |

| Input Voltage               | V <sub>IN</sub>  | -0.5 <sup>1</sup> |     | 7.0 | V     |

| Package Weight              | RSF              |                   | 35  |     | Grams |

| Operating Temperature Range | T <sub>OPR</sub> | -55               |     | 125 | °C    |

| Storage Temperature Range   | T <sub>STG</sub> | -65               |     | 150 | °C    |

<sup>1.</sup>  $V_{IN}$  min = -3.0V for pulse width  $\leq$ 50ns.

TABLE 2. 79C2040 RECOMMENDED DC OPERATING CONDITIONS

| PARAMETER                   | Symbol                                               | Мім                                              | Max                                               | Unit        |

|-----------------------------|------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|-------------|

| Supply Voltage              | V <sub>CC</sub>                                      | 4.5                                              | 5.5                                               | V           |

| Input Voltage RES_PIN       | V <sub>IL</sub><br>V <sub>IH</sub><br>V <sub>H</sub> | -0.3 <sup>1</sup><br>2.2<br>V <sub>CC</sub> -0.5 | 0.8<br>V <sub>CC</sub> +0.3<br>V <sub>CC</sub> +1 | V<br>V<br>V |

| Operating Temperature Range | T <sub>OPR</sub>                                     | -55                                              | 125                                               | °C          |

<sup>1.</sup>  $V_{IL}$  min = -1.0V for pulse width  $\leq$  50 ns

TABLE 3. 79C2040 DELTA LIMITS<sup>1</sup>

| Parameter                          | Variation <sup>2</sup> |

|------------------------------------|------------------------|

| I <sub>CC1A</sub>                  | +/- 10 %               |

| I <sub>CC1D</sub>                  | +/- 10 %               |

| I <sub>CC2A</sub>                  | +/- 10 %               |

| I <sub>LI</sub> - ADDR, CE, OE, WE | +/- 10 %               |

| I <sub>LI</sub> - D0-D39           | +/- 10 %               |

T. Parameters are measured and recorded per MIL-STD-883 for Class K devices

<sup>2.</sup> Specified value in Table 5

### TABLE 4. 79C2040 CAPACITANCE

$(T_A = 25 \, ^{\circ}C, f = 1 \, MHz)$

| Parameter                                              | Symbol                             | Min | Max | Unit |

|--------------------------------------------------------|------------------------------------|-----|-----|------|

| Input Capacitance : V <sub>IN</sub> = 0V <sup>1</sup>  | C <sub>IN</sub> OE                 |     | 6   | pF   |

|                                                        | C <sub>IN</sub> WE                 |     | 6   |      |

|                                                        | C <sub>IN</sub> CE <sub>0-30</sub> |     | 30  |      |

|                                                        | C <sub>IN</sub> A0-A16             |     | 6   |      |

|                                                        | C <sub>IN</sub> RES                |     | 120 |      |

| Output Capacitance: V <sub>OUT</sub> = 0V <sup>1</sup> | C <sub>Out</sub> RDY/BSY           |     | 60  | pF   |

|                                                        | C <sub>O ut</sub> D0-D39           |     | 48  |      |

1. Guaranteed by design.

## Table 5. 79C2040 DC Electrical Characteristics

$(V_{cc} = 5V \pm 10\%, T_A = -55 \text{ to } +125^{\circ}\text{C})$

| Parameter                                        | TEST CONDITION                                                                                                                                  | Symbol                             | Subgroups | Мім                           | Max         | Units       |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------|-------------------------------|-------------|-------------|

| Input Leakage Current<br>A0-A16, WE, OE          | $V_{CC} = 5.5V$ , $V_{IN} = V_{CC} \& V_{IN} = 0V$                                                                                              | ILI                                | 1, 2, 3   |                               | 11          | μA          |

| Input Leakage Current<br>CE                      | V <sub>CC</sub> =5.5V, V <sub>IN</sub> =0V & V <sub>IN</sub> =0V                                                                                |                                    |           |                               | 10          | μA          |

| Input Leakage Current<br>D0-D39                  | $V_{CC}$ =5.5V, $V_{IN}$ = $V_{CC}$ & $V_{IN}$ =0V                                                                                              |                                    |           |                               | 8           | μA          |

| Output LeakageCurrent <sup>1</sup>               | $(V_{CC} = 5.5V, V_{OUT} = 5.5V/0.4V)$                                                                                                          | I <sub>LO</sub>                    | 1, 2, 3   |                               | 8           | μA          |

| Standby V <sub>CC</sub> Current                  | CE = ADDR=WE=OE =V <sub>CC</sub>                                                                                                                | I <sub>CC1A</sub>                  | 1, 2, 3   |                               | 640         | μA          |

|                                                  | CE =V <sub>IH</sub> , ADDR=WE=OE =0V                                                                                                            | I <sub>CC1D</sub>                  |           |                               | 21          | mA          |

| Operating V <sub>CC</sub> Current <sup>1,2</sup> | $\overline{OE} = 0V \ ADDR = \overline{WE} = V_{CC}$<br>$I_{OUT} = 0mA, \overline{CE} \ Duty = 100\%,$<br>$Cycle = 1 \ us \ at \ V_{CC} = 5.5V$ | I <sub>CC2A</sub>                  | 1, 2, 3   |                               | 75          | mA          |

|                                                  | $\overline{OE}$ =ADDR= $\overline{WE}$ =0V<br>$I_{OUT}$ = 0mA, $\overline{CE}$ Duty = 100%,<br>Cycle = 150 ns at $V_{CC}$ = 5.5V                | I <sub>CC2D</sub>                  | 1, 2, 3   |                               | 250         | mA          |

| Input Voltage                                    |                                                                                                                                                 | V <sub>IL</sub><br>V <sub>IH</sub> | 1, 2, 3   | 2.2                           | 0.8         | V           |

| RES_PIN                                          |                                                                                                                                                 | $V_{H}$                            |           | V <sub>CC</sub> -0.5          |             |             |

| Output Voltage <sup>3</sup>                      | Data Lines: $V_{CC}Min$ , $I_{OL}$ = 2.1mA<br>Data Lines: $V_{CC}Min$ , $I_{OH}$ = -400 $\mu$ A<br>All Outputs: $V_{CC}Min$ , $I_{OH}$ = -100uA | V <sub>OL</sub><br>V <sub>OH</sub> | 1, 2, 3   | 2.4<br>V <sub>CC</sub> - 0.3V | 0.4<br><br> | V<br>V<br>V |

<sup>1.</sup> For RES  $I_{IL} = 2000 uA$

<sup>2.</sup> Only one  $\overline{\text{CE}}$  active(Logic Low)

<sup>3.</sup> RBSY is an open drain output. Only  $\boldsymbol{V}_{OL}$  applies to this pin.

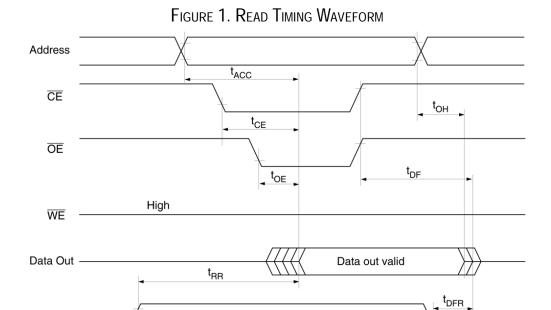

Table 6. 79C2040 AC Electrical Characteristics for Read Operation <sup>1</sup>  $(V_{cc} = 5V \pm 10\%, T_A = -55 \text{ to} + 125^{\circ}\text{C})$

| Parameter                                                                                                                                                    | Symbol           | Subgroups | Min    | Max               | Unit     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------|--------|-------------------|----------|

| Address Access Time $\overline{CE} = \overline{OE} = V_{IL}$ , $\overline{WE} = V_{IH}$ -150 -200                                                            | t <sub>ACC</sub> | 9, 10, 11 | <br>   | 150<br>200        | ns       |

| Chip Enable Access Time $\overline{OE} = V_{IL}$ , $\overline{WE} = V_{IH}$ -150 -200                                                                        | t <sub>CE</sub>  | 9, 10, 11 | <br>   | 150<br>200        | ns       |

| Output Enable Access Time $\overline{CE} = V_{IL}$ , $\overline{WE} = V_{IH}$<br>-150<br>-200                                                                | t <sub>OE</sub>  | 9, 10, 11 | 0<br>0 | 75<br>100         | ns       |

| Output Hold to Address Change $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{JH}$ -150 -200                                                     | t <sub>oH</sub>  | 9, 10, 11 | 0      |                   | ns       |

| Output Disable to High-Z $^2$ $\overline{CE} = V_{IL}$ , $\overline{WE} = V_{IH}$ $-150$ $\overline{CE} = \overline{OE} = V_{IL}$ , $\overline{WE} = V_{IH}$ | t <sub>DF</sub>  | 9, 10, 11 | 0 0    | 50<br>60          | ns<br>ns |

| -150<br>-200<br>RES to Output Delay $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}^3$<br>-150                                               | $T_{RR}$         | 9, 10, 11 | 0 0    | 350<br>450<br>450 | ns       |

| -200                                                                                                                                                         |                  |           | 0      | 650               |          |

<sup>1.</sup> Test conditions: input pulse levels = 0.4V to 2.4V; input rise and fall times ≤ 20 ns; output load = 1 TTL gate + 100 pF (including scope and fixture); reference levels for measuring timing = 0.8 V/1.8 V.

Table 7. 79C2040 AC Electrical Characteristics for Write Operation (V  $_{\text{cc}}$  = 5V  $\pm 10\%$  , T  $_{A}$  = -55 to +125°C)

| Parameter                                                 | Symbol          | Subgroups | M <sub>IN</sub> <sup>1</sup> | Max | Units |

|-----------------------------------------------------------|-----------------|-----------|------------------------------|-----|-------|

| Address Setup Time -150 -200                              | t <sub>AS</sub> | 9, 10, 11 | 0                            |     | ns    |

| Chip Enable to Write Setup Time (WE controlled) -150 -200 | t <sub>CS</sub> | 9, 10, 11 | 0                            |     | ns    |

<sup>2.</sup>  $t_{DF}$  and  $t_{DFR}$  are defined as the time at which the output becomes an open circuit and data is no longer driven.

<sup>3.</sup> Guaranteed by design.

Table 7. 79C2040 AC Electrical Characteristics for Write Operation ( $V_{cc}$  = 5V ±10%,  $T_A$  = -55 to +125°C)

|                                                              | E 10%, 1 <sub>A</sub> = -33 10 |           | N a - 1           | B A      |          |

|--------------------------------------------------------------|--------------------------------|-----------|-------------------|----------|----------|

| Parameter                                                    | Symbol                         | Subgroups | Min <sup>1</sup>  | Max      | Units    |

| Write Pulse Width CE controlled -150 -200 WE controlled -150 | t <sub>CW</sub>                | 9, 10, 11 | 250<br>350<br>250 | <br>     | ns<br>ns |

| -200                                                         |                                |           | 350               |          |          |

| Address Hold Time<br>-150<br>-200                            | t <sub>AH</sub>                | 9, 10, 11 | 150<br>200        |          | ns       |

| Data Setup Time<br>-150<br>-200                              | t <sub>DS</sub>                | 9, 10, 11 | 100<br>150        |          | ns       |

| Data Hold Time<br>-150<br>-200                               | t <sub>DH</sub>                | 9, 10, 11 | 10<br>10          |          | ns       |

| Chip Enable Hold Time (WE controlled)<br>-150<br>-200        | t <sub>CH</sub>                | 9, 10, 11 | 0<br>0            |          | ns       |

| Write Enable to Write Setup Time (CE controlled) -150 -200   | t <sub>WS</sub>                | 9, 10, 11 | 0<br>0            |          | ns       |

| Write Enable Hold Time (CE controlled) -150 -200             | t <sub>WH</sub>                | 9, 10, 11 | 0<br>0            |          | ns       |

| Output Enable to Write Setup Time -150 -200                  | t <sub>OES</sub>               | 9, 10, 11 | 0<br>0            |          | ns       |

| Output Enable Hold Time<br>-150<br>-200                      | t <sub>OEH</sub>               | 9, 10, 11 | 0<br>0            |          | ns       |

| Write Cycle Time <sup>2</sup> -150 -200                      | t <sub>WC</sub>                | 9, 10, 11 | <br>              | 10<br>10 | ms       |

| Data Latch Time<br>-150<br>-200                              | t <sub>DL</sub>                | 9, 10, 11 | 300<br>400        |          | ns       |

| Byte Load Window<br>-150<br>-200                             | t <sub>BL</sub>                | 9, 10, 11 | 100<br>200        |          | μs       |

| Byte Load Cycle<br>-150<br>-200                              | t <sub>BLC</sub>               | 9, 10, 11 | .55<br>.95        | 30<br>30 | μs       |

04.20.05 Rev 1

All data sheets are subject to change without notice

Table 7. 79C2040 AC Electrical Characteristics for Write Operation ( $V_{cc}$  = 5V  $\pm 10\%$ ,  $T_A$  = -55 to +125°C)

| Parameter                                                | Symbol           | Subgroups | Min <sup>1</sup> | Max | Units |

|----------------------------------------------------------|------------------|-----------|------------------|-----|-------|

| Time to Device Busy -150 -200                            | t <sub>DB</sub>  | 9, 10, 11 | 120<br>170       |     | ns    |

| Write Start Time <sup>3</sup> -150 -200                  | t <sub>DW</sub>  | 9, 10, 11 | 150<br>250       |     | ns    |

| RES to Write Setup Time <sup>4</sup> -150 -200           | t <sub>RP</sub>  | 9, 10, 11 | 100<br>200       |     | μs    |

| V <sub>CC</sub> to RES Setup Time <sup>4</sup> -150 -200 | t <sub>RES</sub> | 9, 10, 11 | 1 3              |     | μs    |

- 1. Use this device in a longer cycle than this value.

- 2. t<sub>WC</sub> must be longer than this value unless polling techniques or RDY/BUSY are used. This device automatically completes the internal write operation within this value.

- 3. Next read or write operation can be initiated after  $t_{\text{DW}}$  if polling techniques or RDY/BUSY are used.

- 4. Guaranteed by design.

TABLE 8. 79C2040 Mode Selection <sup>1</sup>

| PARAMETER     | CE 2            | ŌE              | WE              | I/O                   | RES            | RDY/BUSY                |

|---------------|-----------------|-----------------|-----------------|-----------------------|----------------|-------------------------|

| Read          | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | D <sub>OUT</sub>      | V <sub>H</sub> | High-Z                  |

| Standby       | V <sub>IH</sub> | Х               | Х               | High-Z                | Х              | High-Z                  |

| Write         | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | D <sub>IN</sub>       | $V_{H}$        | High-Z> V <sub>OL</sub> |

| Deselect      | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | High-Z                | $V_{H}$        | High-Z                  |

| Write Inhibit | Х               | Х               | V <sub>IH</sub> |                       | Х              |                         |

|               | Х               | V <sub>IL</sub> | Х               |                       | Х              |                         |

| Data Polling  | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | Data Out <sup>3</sup> | $V_{H}$        | V <sub>OL</sub>         |

| Program Reset | Х               | Х               | Х               | High-Z                | V <sub>L</sub> | High-Z                  |

- T. Refer to the recommended DC operating conditions.

- 2. For  $\overline{\text{CE}}_{0.3}$  only one  $\overline{\text{CE}}$  can be used (active) at a time.

- 3. Bits 7, 15, 23, 31 and 39

RES

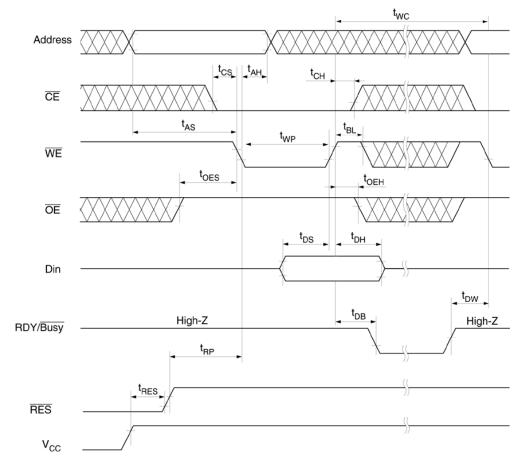

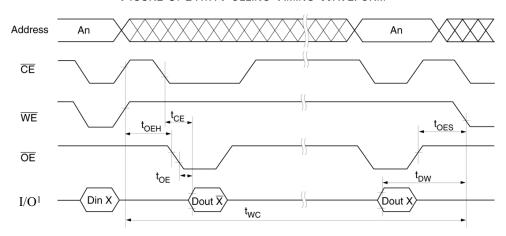

FIGURE 2. BYTE WRITE TIMING WAVEFORM (1) (WE CONTROLLED)

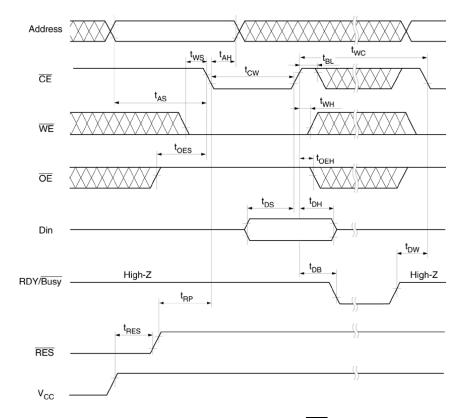

FIGURE 3. BYTE WRITE TIMING WAVEFORM (2) (CE CONTROLLED)

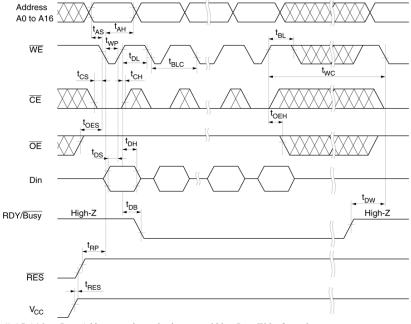

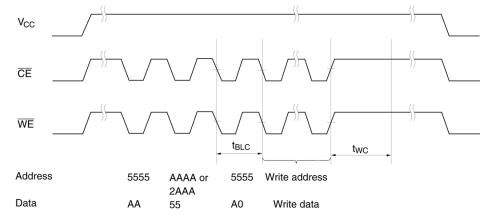

FIGURE 4. PAGE WRITE TIMING WAVEFORM (1) (WE CONTROLLED)

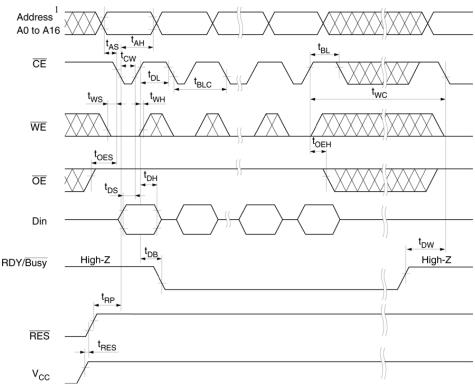

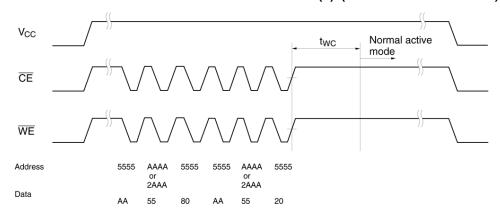

FIGURE 5. PAGE WRITE TIMING WAVEFORM (2) (CE CONTROLLED)

1) A7-A16 are Page Addresses and must be the same within a Page Write Operation.

FIGURE 6. DATA POLLING TIMING WAVEFORM

1) I/O 7, 15, 23, 31 AAND 39

FIGURE 7. SOFTWARE DATA PROTECTION TIMING WAVEFORM (1) (IN PROTECTION MODE)

FIGURE 8. SOFTWARE DATA PROTECTION WAVEFORM (2) (IN NON-PROTECTION MODE)

## **EEPROM APPLICATION NOTES**

This application note describes the programming procedures for the EEPROM modules and with details of various techniques to preserve data integrity.

#### **Automatic Page Write**

Page-mode write feature allows 1 to 128 bytes of data to be written into the EEPROM in a single write cycle. Loading the first byte of data, the data load window opens  $30\mu$ s for the second byte. In the same manner each additional byte of data can be loaded within  $30\mu$ s of the preceding falling edge of either WE or CE. When CE and WE are kept high for  $100\mu$ s after data input, the EEPROM enters the write mode automatically and the data input is written into the EEPROM.

## WE, CE Pin Operation

<u>During a write cycle</u>, addresses are latched by the falling edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ , and data is latched by the rising edge of  $\overline{\text{WE}}$  or  $\overline{\text{CE}}$ .

#### **Data Polling**

Data Polling function allows the status of the EEPROM to be determined. If EEPROM is set to read mode during a write cycle, an inversion of the last byte of data to be loaded outputs from I/O 7 to indicate that the EEPROM is performing a write operation.

### RDY/Busy Signal

RDY/Busy signal also allows a comparison operation to determine the status of the EEPROM. The RDY/Busy signal goes low ( $V_{OL}$ ) after the first write signal. At the end of the write cycle, the RDY/Busy returns to a high state.

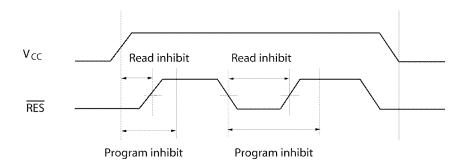

### **RES** Signal

When  $\overline{RES}$  is LOW (V<sub>L</sub>), the EEPROM cannot be read or programmed. The EEPROM data must be protected by keeping  $\overline{RES}$  low when V<sub>CC</sub> is power on and off.  $\overline{RES}$  should be high (V<sub>H</sub>) during read and programming operations.

#### **Data Protection**

To protect the data during operation and power on/off, the EEPROM has the internal functions described below.

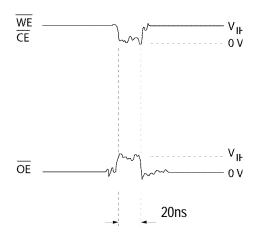

1. Data Protection against Noise of Control Pins (CE, OE, WE) during Operation.

During readout or standby, noise on the control pins may act as a trigger and turn the EEPROM to programming mode by mistake. To prevent this phenomenon, the EEPROM has a noise cancellation function that cuts noise if its width is 20ns or less in programming mode. Be careful not to allow noise of a width more than 20ns on the control pins.

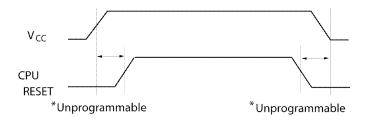

### 2. Data Protection at V<sub>CC</sub> on/off

When  $V_{CC}$  is turned on or off, noise on the control pins generated by external circuits, such as CPUs, may turn the EEPROM to programming mode by mistake. To prevent this unintentional programming, the EEPROM must be kept in unprogrammable state during  $V_{CC}$  on/off by using a CPU reset signal to  $\overline{RES}$  pin.

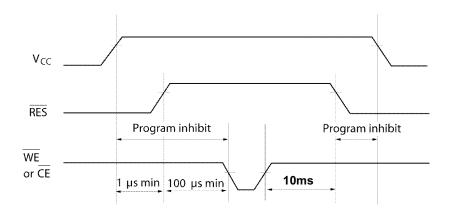

## 3. RES Signal

$\overline{RES}$  should be kept at  $V_{SS}$  level when  $V_{CC}$  is turned on or off. The EEPROM breaks off programming operation when  $\overline{RES}$  become low, programming operation doesn't finish correctly in case that  $\overline{RES}$  falls low during programming operation.  $\overline{RES}$  should be kept high for 10 ms after the last data is input

#### 4. Software Data Protection Enable

The 79C2040 contains a software controlled write protection feature that allows the user to inhibit all write operations to the device. This is useful in protecting the device from unwanted write cycles due to uncontrollable circuit noise or inadvertent writes caused by minor bus contentions. Software data protection is enabled by writing the following data sequence to the EEPROM and allowing the write cycle period ( $t_{WC}$ ) of 10ms to elapse:

#### Software Data Protection Enable Sequence

| Address      | Data           |

|--------------|----------------|

| 5555         | AA AA AA AA    |

| AAAA or 2AAA | 55 55 55 55 55 |

| 5555         | A0 A0 A0 A0 A0 |

04.20.05 Rev 1

All data sheets are subject to change without notice

### 5. Writing to the Memory with Software Data Protection Enabled

To write to the device once Software protection is enabled, the enable sequence must precede the data to be written. This sequence allows the write to occur while at the same time keeping the software protection enabled

#### Sequence for Writing Data with Software Protection Enabled.

| Address          | Data              |  |

|------------------|-------------------|--|

| 5555             | AA AA AA AA       |  |

| AAAA or 2AAA     | 55 55 55 55       |  |

| 5555             | A0 A0 A0 A0 A0    |  |

| Write Address(s) | Normal Data Input |  |

#### 6. Disabling Software Protection

Software data protection mode can be disabled by inputting the following 6 bytes sequence. Once the software protection sequence has been written, no data can be written to the memory until the write cycle (T<sub>wc</sub>) has elapsed.

#### Software Protection Disable Sequence

| Address      | Data           |  |  |

|--------------|----------------|--|--|

| 5555         | AA AA AA AA    |  |  |

| AAAA or 2AAA | 55 55 55 55 55 |  |  |

| 5555         | 80 80 80 80 80 |  |  |

| 5555         | AA AA AA AA    |  |  |

| AAAA or 2AAA | 55 55 55 55 55 |  |  |

| 5555         | 20 20 20 20 20 |  |  |

Devices are shipped in the "unprotected" state, meaning that the contents of the memory can be changed as required by the user. After the software data protection is enabled, the device enters the Protect Mode where no further write commands have any effect on the memory contents.

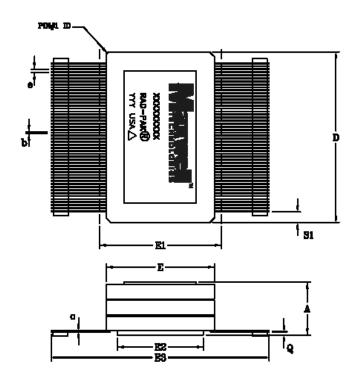

100 PIN STACKED FLAT PACKAGE

| Sүмвоl | Dimension |       |       |

|--------|-----------|-------|-------|

|        | Min       | Nом   | Max   |

| А      | .400      | .448  | .500  |

| b      | .006      | .008  | .010  |

| С      | .006      | .008  | .010  |

| D      | 1.346     | 1.366 | 1.388 |

| E      | .882      | .897  | .912  |

| E1     |           |       | .950  |

| E2     | .702      | .708  |       |

| E3     | 1.825     | 1.900 |       |

| е      | 0.025BSC  |       |       |

| L      | .330      | .340  | .350  |

| Q      | .013      | .018  | .023  |

| S1     | .005      | .075  |       |

| N      | 100       |       |       |

Note: All dimensions in inches

## **79C2040**

## 20 Megabit (512 x 40-Bit) EEPROM MCM

#### Important Notice:

These data sheets are created using the chip manufacturers published specifications. Maxwell Technologies verifies functionality by testing key parameters either by 100% testing, sample testing or characterization.

The specifications presented within these data sheets represent the latest and most accurate information available to date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no responsibility for the use of this information.

Maxwell Technologies' products are not authorized for use as critical components in life support devices or systems without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days from the date of shipment from Maxwell Technologies. Maxwell Technologies' liability shall be limited to replacement of defective parts.